外媒称三星电子正计划将BSPDN技术用于2nm制程工艺

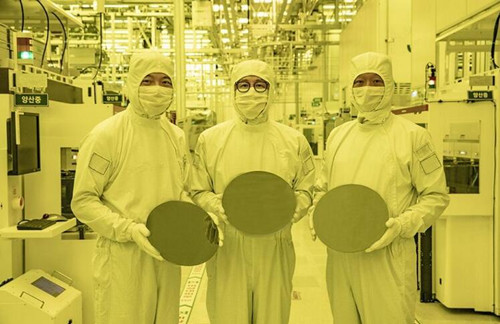

10月14日消息,据国外媒体报道,三星电子采用全环绕栅极晶体管架构的3nm制程工艺,已在6月30日开始初步生产芯片,所代工的首批晶圆,在7月25日正式发货。在3nm制程工艺开始量产之后,三星电子芯片制程工艺研发的重点,就将集中在更先进的2nm制程工艺上。

对于三星电子的2nm制程工艺,有外媒在报道中称,他们正计划将背面供电网络 (BSPDN) 这一技术,用于2nm制程工艺。

从外媒的报道来看,三星的研究员Park Byung-jae,在上周的SEDEX 2022上就介绍了这一技术,他表示在晶圆代工方面,技术从高k金属栅极平面FET发展到FinFET(鳍式场效应晶体管),再到MBCFET(多桥通道场效应晶体管),现在则是BSPDN。

不过,与10nm制程工艺开始采用的FinFET和3nm制程工艺开始采用的MBCFET技术不同,背面供电网络并不是晶体管架构技术,它是将供电网络从前端移动移到后端的技术,利用芯片的背面。

背面供电网络技术,最初是在2019年作为一种概念推出的,而在2021年,公开的一篇有关2nm制程工艺技术的论文中,引用了这一技术。

论文的数据表明,同将供电网络布局在正面相比,采用背面供电网络技术的2nm制程工艺,可使芯片的性能提升44%,能效提升30%。论文还指出,将供电网络等功能移至芯片的背面,能解决仅使用正面造成的布线堵塞问题。